3D 적층 구조에 대하여 : 리사 수는 신이다

GENo07

·2024. 12. 26. 16:51

이 글은 직접 만든 PPT를 바탕으로 Perplexity를 활용하여 작성된 글입니다.

안녕하세요 ITLover0의 GENo07입니다.

오늘은 3D 집적 기술의 수학적 모델링에 대해 자세히 알아보겠습니다.

들어가며: 3D 집적 기술과 수학의 만남

반도체 업계는 오랫동안 '무어의 법칙'을 따라 발전해왔습니다. 하지만 평면 구조에서의 미세화가 물리적 한계에 도달하면서, 수직 방향으로의 확장이 새로운 돌파구로 떠올랐습니다. 이러한 3D 집적 기술을 구현하기 위해서는 복잡한 수학적 모델링이 필수적입니다.

수학적 모델링의 핵심 요소

1. 구조 해석 모델링

가장 기본이 되는 것은 유한요소법(FEM)입니다. 무한개의 절점과 자유도를 유한개로 전환하여 선형 연립방정식으로 구성하는 방식인데요. 주요 구조 해석 요소로는 포와송 비(Poisson's Ratio), 열팽창 계수(CTE), 응력(Stress) 등이 있습니다.

2. 전기적 모델링

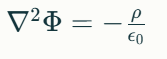

푸아송 방정식이 핵심입니다.

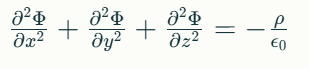

여기서 라플라시안 연산자(∇²)는 3차원 공간에서 다음과 같이 전개됩니다:

이 방정식은 다음과 같은 용도로 활용됩니다:

- 3D 구조에서의 전하 분포와 전기장 해석

- TSV 주변의 전기장 및 전위 분포 계산

- 실리콘 기판과 TSV 사이의 MOS 구조 모델링

3. 열 해석 모델링

패키지의 주요 온도 지점을 정의하여 분석합니다:

- 주변 온도(Ta)

- 정션 온도(Tj)

- 케이스 온도(Tc)

- 보드 온도(Tb)

4. 적층 공정 모델링

곡선 길이 계산을 위한 적분식:

s(t)=∫0tx˙(u)+y˙(u)+z˙(u)du

실제 적용 사례

AMD의 혁신

AMD는 3D V-Cache 기술을 통해 CPU 다이 위에 캐시 메모리를 수직으로 쌓는데 성공했습니다. 이 과정에서 TSV를 통한 수직 연결이 핵심이었는데요, 이를 위해 복잡한 전기적 모델링이 필요했습니다.

삼성전자의 V-NAND

현재 236층까지 구현된 V-NAND는 수학적 모델링의 승리라고 할 수 있습니다. 특히 층간 간섭을 최소화하기 위한 전자기장 해석이 중요했습니다.

향후 과제와 전망

기술적 과제

- 열 관리 문제

- 수직 적층으로 인한 발열량 증가

- 새로운 냉각 솔루션 필요

- 신뢰성 검증

- 층간 접합 강도 분석

- 열응력 시뮬레이션

미래 전망

- 인텔: 2030년까지 패키지당 1조 개 트랜지스터 구현 목표

- TSMC: 첨단 패키징 기술과 3D IC 기술 개발

- AMD: 3D V-Cache 기술 확대 적용

마치며

3D 집적 기술은 단순한 물리적 적층이 아닌, 복잡한 수학적 원리들의 집합체입니다. 앞으로도 이 기술은 계속 발전할 것이며, 그 핵심에는 항상 수학적 모델링이 있을 것입니다.다음에는 3D 집적 기술의 신뢰성 검증을 위한 구체적인 수치 해석 방법에 대해 알아보도록 하겠습니다.